Summary

This paper introduces a face-down, bumpless Chip-on-Wafer (COW) bonding method using a waffle-wafer structure. The technique removes the need for traditional solder bumps and enables heterogeneous chip assembly with improved alignment accuracy. The authors demonstrate successful bonding performance and discuss how this approach can support higher-density 3D integration while reducing thermal and mechanical stress during packaging.

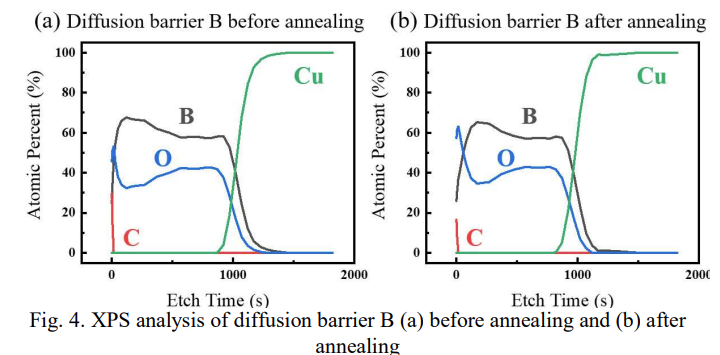

Figure 4 – XPS Analysis of Diffusion Barrier B

Key Concepts

- Bumpless bonding compared to traditional solder bump methods.

- Waffle-wafer structure for high alignment accuracy.

- Implications for high-density 3D integration.

- Reduced thermal and mechanical stress in packaging.

Example Application Scenario

This technique can be applied to advanced logic–memory stacking, where precise alignment and minimal thermal budget are critical to performance and reliability.